Technologies successfully developed and transferred/ demonstrated include:

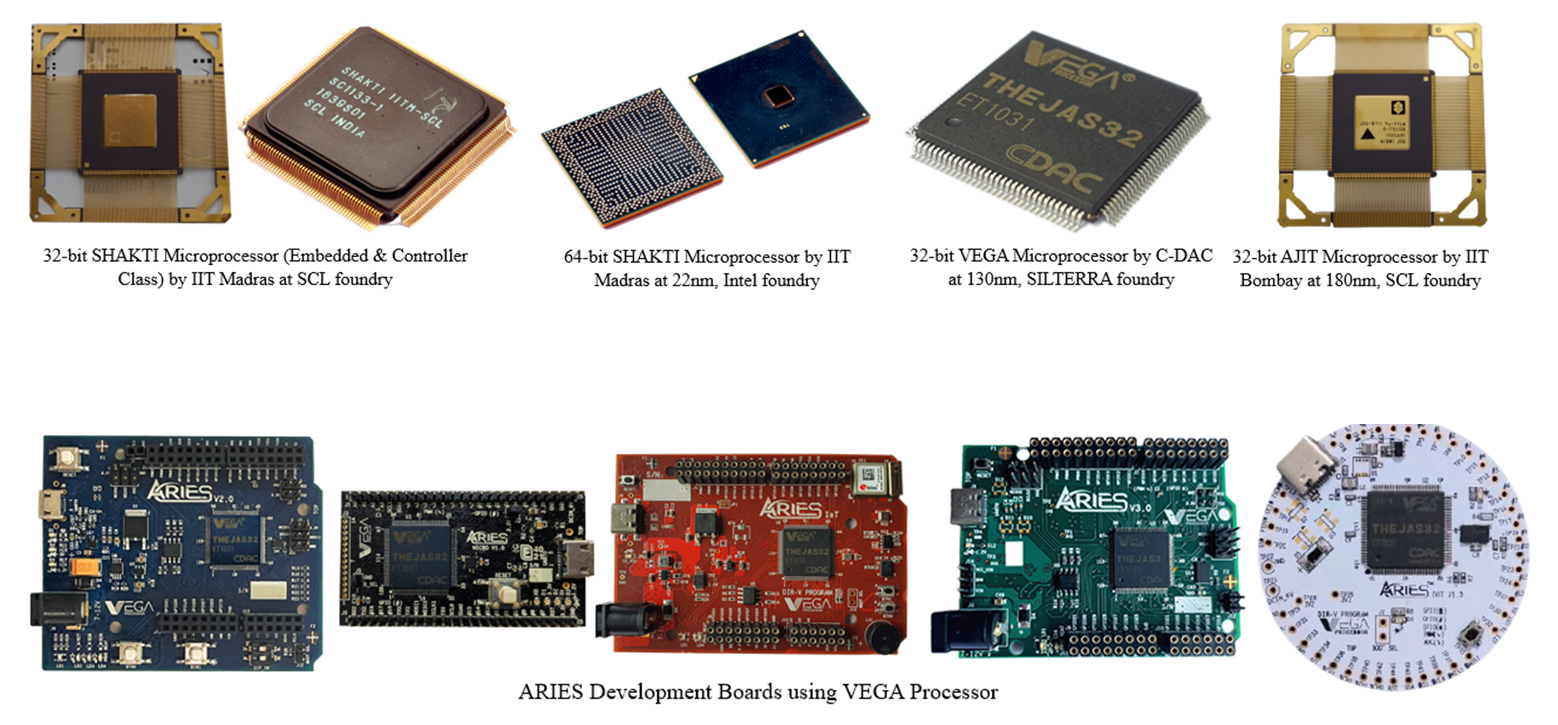

- Microprocessor Development Programme: Family of 32-bit/ 64-bit Microprocessor being indigenously designed using Open-Source ISA (Instruction Set Architecture) and fabricated them along with developing reusable IP Cores and hardware development baords by C-DAC, IIT Madras & IIT Bombay. Details here and here.

MoU has been signed by Aheesa Digital Innovations and Calligo Technologies for using VEGA Processor in their SoC devices. SHAKTI Processor is being explored for usage by the strategic sector.

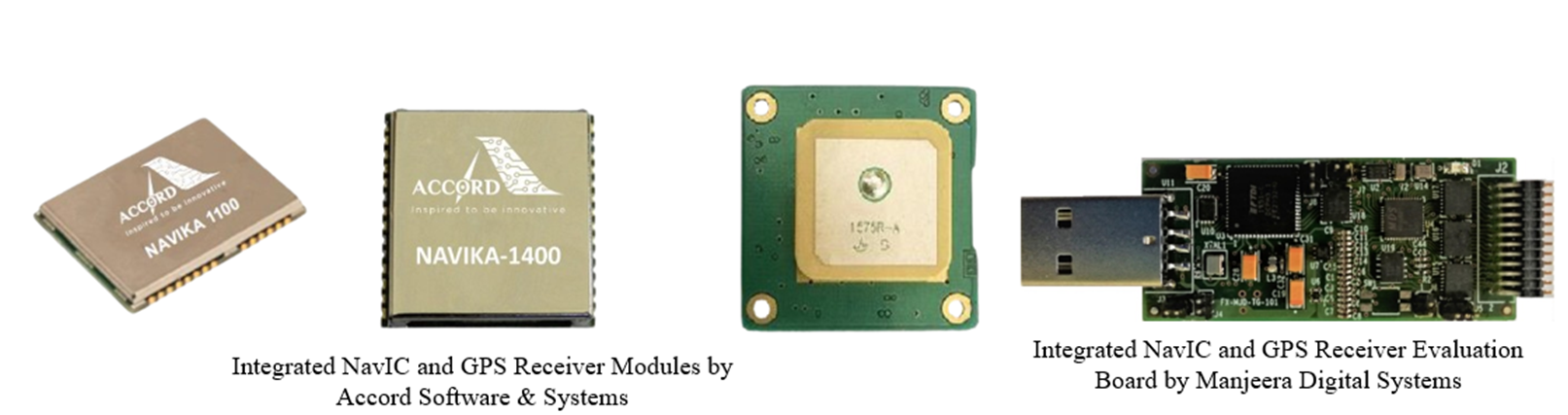

MoU has been signed by Aheesa Digital Innovations and Calligo Technologies for using VEGA Processor in their SoC devices. SHAKTI Processor is being explored for usage by the strategic sector. - Design & development of NavIC Receiver: For effective use of Navigational services based on Indian Constellation of Satellites, named NavIC (Navigation with Indian Constellation), integrated NavIC and GPS Receiver Modules have been designed and fabricated for civilian use in various application sector.

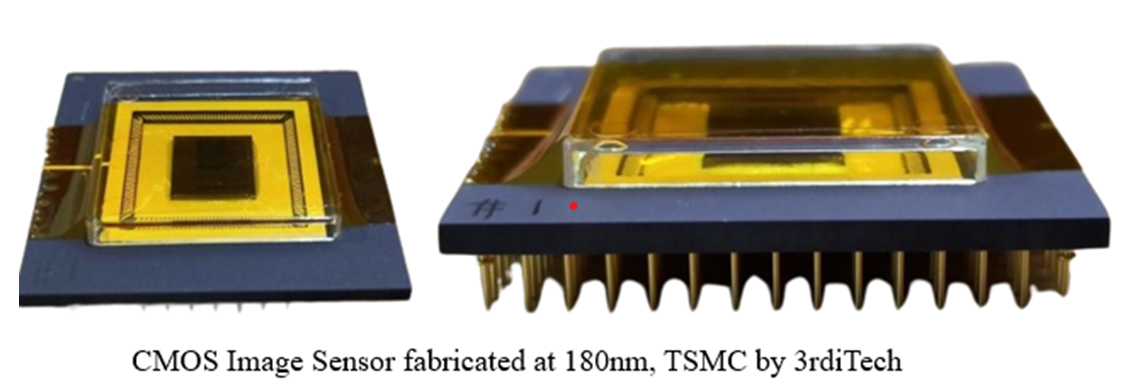

- Low-light High-resolution CMOS Image Sensor Low-light CMOS Image Sensor with Single Photon Detection has been designed and fabricated at 180nm, TSMC by 3rdiTech for Security, Surveillance, Automobile Cameras.

- Digital Programmable Hearing Aid An ASIC based Digital Programmable Hearing Aid (DPHA) named TARANG along with hearing aid programming software has been designed and developed by CDAC Thiruvananthapuram. TARANG, available as Body-Worn (BW) and Behind-the-Ear (BTE) models, is suitable for hearing impaired patients with mild, moderate and profound hearing loss. The project won the National Award instituted by Ministry of Social Justice & Empowerment, Govt. of India for "Development of Best product and technology to empower physically impaired persons". The technology has been transferred to M/S Best Hearing Solutions, Delhi and M/S Keltron, Kerala and over 100,000 units have been sold till date.

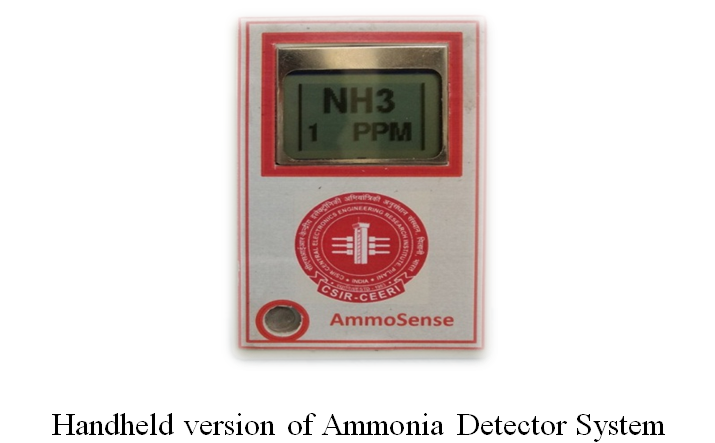

- Micro-Electrical Mechanical Systems (MEMS) based Gas sensors MEMS based Integrated Micro Gas Sensor for detection of Ammonia gas developed by CEERI Pilani. The technology has been transferred to M/s Macwin India.

- Low-Temperature and Low-Pressure Cu-Cu Thermo-Compression Bonding for Vertical (3-D) Integration The technology for Low-Temperature and Low-Pressure Cu-Cu Thermo-Compression Bonding Technique for Vertical (3-D) Integration developed by IIT-Hyderabad. The technology has been transferred to M/s Solidblocks Semiconductor Solutions Pvt. Ltd.

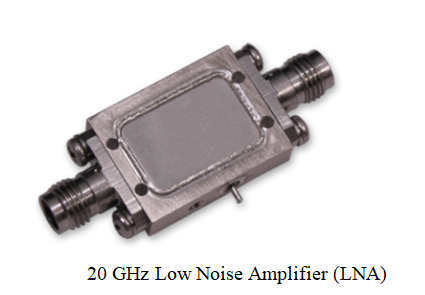

- 20 GHz Low Noise Amplifier (LNA) 20 GHz Low Noise Amplifier (LNA) technology for amplification of weak RF signal developed by IISc Bangalore. Field trial of the prototype carried out successfully.

- Patents Several Patents have been filed/ being filed under the projects sponsored by Microelectronics Development not limited to the following:

1. Optimized ultra-thin alloys leads sub 140 degree Celsius and Low Pressure 2.5 bar Cu-Cu bonding for 3D ICs- IIT Hyderabad

2. A Handheld Battery-Operated Pulse Oximeter Recording and Analysis System- IIT Bombay

3. Establishing communication between transmitter and receiver in MedRadio Spectrum band- IIT Bombay

4. SAW Resonator Oscillator Based Injection Locked OOK Transmitter- IIT Bombay

5. A design method for low-power low-noise biomedical signal conditioning circuit with extracted noise and mismatch parameters- IIT Bombay

6. Low Phase Noise Quadrature Oscillators- IIT Madras

7. Phase Error Measurement Circuit with Reference less Gain and Offset-Calibration- IIT Madras

8. Low Power Continuous - Time Delta-Sigma Converters (Indian and International Patent)- IIT Madras

9. Novel subtractive process for easy patterning of printed thick films in LTCC- CMET Pune

10. Fine Laser patterning of printed thick films on LTCC- CMET Pune

11. Syringe dispensing method and compatible silver paste for direct writing of patterns on LTCC- CMET Pune

12. Sub 1000C Thermo-compression metal-metal direct bonding (Indian patent) - IIT Hyderabad.

13. CMOS wideband RF amplifier with gain roll-off compensation for external parasitics

14. Methods and apparatus for reduction of motion artifact and noise in ECG signal

15. Continuously variable precision and linear floating resistor using metal-oxide-semiconductor field-effect transistors

16. A current source array for high-resolution high-speed digital to Analog converters

17. A lateral DMOS transistor and method of fabricating thereof

18. An ultra-low power, read decoupled-differential write, 10t sram cell with larger read/write noise margin

19. Offset compensated data sensing technique for low energy embedded RAM

20. On-Chip Jitter measurement circuit for high-speed data and clock, high-speed voltage controlled CML hysteresis delay cell and ring oscillator using the same, low power high dynamic range programmable gain amplifier

21. Ultra-low trans conductance amplifier using carbon nano tube field effect transistor

22. Power supply noise reduction using clock gating with variable frequency as global clock

23. N-stage OTA buffer amplifiers with unity gain and high input dynamic range and tunable gain for driving large resistance loads

24. Internet of things enabled energy management system

25. Method and System for enriching life in a humanly maintained aquaculture environment

26. A novel microfluidic approach for bio-mems applications

27. Fully differential clocked comparator for pipelined analog - to - digital converter

28. A Scalable compact digital-in concept comparator for adc

29. Polymer electrostatic mems cantilever beam

30. High speed voltage controlled cml hysteresis delay cell and ring oscillator using the same

31. An auxiliary circuit in Analog-to-Digital Converter for adaptive sampling architecture.

32. Amplitude dependent variable sampling frequency-based sigma delta modulator

33. Reconfigurable and unified signal processing apparatus for generating variable length Hamming and Hanning window functions - Publications Over 2000 research papers have been published in the reputed Journals/ Conference proceedings under the projects sponsored by Microelectronics Development Division.

- Industry-ready manpower About 75,000 industry-ready manpower at B.Tech, M.Tech and PhD level generated in VLSI/ Chip design area by way of designing working prototype of ASICs/ SoCs. Details here.